Upgrade & Secure Your Future with DevOps, SRE, DevSecOps, MLOps!

We spend hours scrolling social media and waste money on things we forget, but won’t spend 30 minutes a day earning certifications that can change our lives.

Master in DevOps, SRE, DevSecOps & MLOps by DevOps School!

Learn from Guru Rajesh Kumar and double your salary in just one year.

Introduction

IC Design & Verification Tools help semiconductor engineers design, simulate, verify, validate, and prepare integrated circuits for manufacturing. In simple words, these tools are used to create chips, test whether the design behaves correctly, check timing and power, validate physical layout, and reduce the risk of silicon failure before fabrication.

This category matters more because chips are now used in almost every advanced product, including AI systems, smartphones, electric vehicles, medical devices, telecom infrastructure, industrial automation, aerospace systems, and edge computing devices. Modern IC teams must manage complex SoCs, advanced verification needs, power limits, security concerns, functional safety, and faster tape-out timelines.

Common use cases include:

- ASIC and SoC design

- RTL simulation and verification

- Logic synthesis and physical implementation

- Formal verification and static checks

- Timing, power, and signal integrity analysis

- Design-for-test and scan insertion

- FPGA prototyping and emulation

- Analog, mixed-signal, and custom IC design

Buyers should evaluate:

- RTL simulation depth

- Formal verification capabilities

- Synthesis and implementation flow

- Physical design and signoff support

- Debugging and waveform analysis

- UVM/SystemVerilog support

- Analog and mixed-signal capabilities

- Foundry and IP ecosystem support

- Scalability for large chip projects

- Security, licensing, and support model

Best for: Semiconductor companies, chip design teams, ASIC engineers, verification engineers, SoC architects, FPGA teams, EDA managers, research labs, AI hardware companies, automotive electronics teams, telecom hardware companies, and enterprise product engineering teams.

Not ideal for: Teams that only need simple PCB design, basic circuit diagrams, low-complexity embedded boards, or beginner electronics learning. For those needs, PCB design software, circuit simulators, or educational electronics tools may be better.

Key Trends in IC Design & Verification Tools

- AI-assisted EDA is becoming more useful: Modern IC design teams are using AI-assisted flows for design-space exploration, faster debugging, verification productivity, optimization, and repetitive task automation.

- Verification workload keeps increasing: Verification often consumes a large part of chip development effort, so simulation acceleration, formal methods, coverage closure, and reusable verification IP are becoming more important.

- Chiplet and advanced packaging workflows are growing: IC design is moving beyond single-die thinking. Teams increasingly need package-aware design, die-to-die interfaces, thermal checks, and system-level verification.

- Power, performance, and area optimization remains critical: AI, mobile, automotive, and edge devices require careful trade-offs between speed, power consumption, heat, and silicon area.

- Cloud and hybrid compute models are expanding: Large verification and simulation workloads need scalable compute. Many organizations use hybrid infrastructure to manage peak workloads.

- Security-by-design is becoming a buying factor: Chip designs contain valuable IP, so buyers are reviewing access control, license governance, project isolation, encryption, and secure collaboration.

- Open-source silicon design is gaining attention: Open-source tools are not replacing enterprise EDA for advanced commercial chips, but they are useful for education, research, prototyping, and smaller digital design flows.

- Functional safety and compliance needs are rising: Automotive, aerospace, medical, and industrial chips require stronger traceability, verification discipline, documentation, and signoff confidence.

- Design-for-test is more important: As chips grow more complex, test coverage, scan insertion, built-in self-test, and manufacturing defect detection are essential.

- Interoperability remains a major concern: IC teams depend on Verilog, SystemVerilog, VHDL, SPICE, Liberty, LEF/DEF, UPF, SDC, GDSII, OASIS, IP-XACT, and foundry-specific flows.

How We Selected These Tools

The tools below were selected using a practical semiconductor buyer-focused evaluation method:

- Strong market recognition in IC design, verification, simulation, or physical implementation

- Feature completeness for ASIC, SoC, FPGA, analog, mixed-signal, or verification workflows

- Adoption by professional semiconductor, electronics, or advanced hardware teams

- Relevance to modern chip design flows, including AI, cloud, chiplets, and advanced verification

- Reliability and performance signals for large-scale design and verification workloads

- Ecosystem strength, including foundry support, IP support, partner tools, and integrations

- Fit across enterprise, mid-market semiconductor teams, startups, research teams, and open-source users

- Support for modern verification methods such as UVM, formal verification, coverage, and emulation

- Availability of documentation, training, onboarding, and vendor support

- Balanced inclusion of enterprise EDA suites, verification tools, FPGA flows, and open-source options

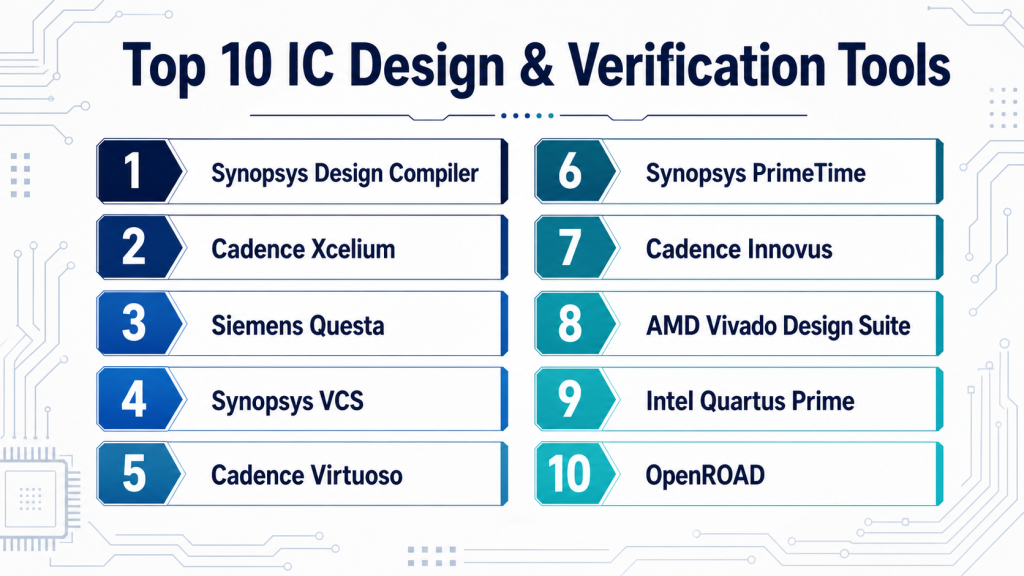

Top 10 IC Design & Verification Tools

#1 — Synopsys Design Compiler

Short description : Synopsys Design Compiler is a widely recognized logic synthesis tool used to convert RTL designs into optimized gate-level netlists. It is mainly used by ASIC and SoC design teams that need production-grade synthesis quality, timing control, and integration with signoff flows.

Key Features

- RTL-to-gate logic synthesis

- Timing-driven optimization

- Area and power optimization support

- Constraint-based design flow

- Integration with Synopsys digital implementation tools

- Support for standard cell libraries

- Suitable for large ASIC and SoC projects

Pros

- Strong industry adoption in ASIC flows

- Mature synthesis capability for production chip design

- Good fit for structured enterprise semiconductor workflows

Cons

- Expensive for small teams and research-only users

- Requires experienced digital design engineers

- Works best inside a broader Synopsys or enterprise EDA flow

Platforms / Deployment

Linux

Self-hosted / Hybrid options vary by enterprise environment

Security & Compliance

SSO/SAML, MFA, encryption, audit logs, RBAC: Varies by enterprise infrastructure and license setup.

SOC 2, ISO 27001, GDPR, HIPAA: Not publicly stated.

Integrations & Ecosystem

Design Compiler is commonly used as part of a larger ASIC flow. It connects with RTL design, verification, timing constraints, physical implementation, and signoff tools.

- RTL design workflows

- Standard cell library support

- Synopsys digital design ecosystem

- Static timing analysis tools

- Power intent workflows

- Physical design handoff

Support & Community

Synopsys provides enterprise documentation, support, training, and professional services. The tool is mostly used by professional chip design teams rather than casual users.

#2 — Cadence Xcelium

Short description : Cadence Xcelium is a simulation and verification platform used for RTL simulation, SystemVerilog verification, UVM environments, low-power verification, and mixed-language design flows. It is suitable for ASIC, SoC, IP, and complex digital verification teams.

Key Features

- RTL simulation

- SystemVerilog and UVM support

- Mixed-language verification support

- Coverage-driven verification workflows

- Low-power verification support

- Debug and waveform analysis integration

- Scalable verification performance options

Pros

- Strong fit for modern verification teams

- Good support for UVM-based verification environments

- Useful for large ASIC and SoC verification projects

Cons

- Requires verification expertise

- Licensing cost can be high for smaller teams

- Best value comes when used with a complete Cadence verification flow

Platforms / Deployment

Linux

Self-hosted / Hybrid options vary

Security & Compliance

SSO/SAML, MFA, encryption, audit logs, RBAC: Varies by enterprise configuration.

SOC 2, ISO 27001, GDPR, HIPAA: Not publicly stated.

Integrations & Ecosystem

Xcelium works within Cadence’s broader verification and design ecosystem. It is often used with coverage tools, debug tools, formal verification, emulation, and regression environments.

- Cadence verification ecosystem

- UVM testbench flows

- Coverage and debug tools

- Low-power verification

- Regression management systems

- Mixed-language design flows

Support & Community

Cadence provides enterprise support, technical documentation, training, and customer assistance. Community knowledge is strong among professional verification engineers.

#3 — Siemens Questa

Short description: Siemens Questa is a verification platform used for simulation, formal verification, coverage, low-power verification, CDC analysis, and verification management. It is widely used by ASIC, FPGA, SoC, and IP verification teams.

Key Features

- RTL simulation and debugging

- SystemVerilog and UVM support

- Formal verification options

- CDC and RDC verification support

- Coverage and verification management

- Low-power verification workflows

- FPGA and ASIC verification support

Pros

- Strong verification breadth

- Useful for both ASIC and FPGA teams

- Mature support for advanced verification methods

Cons

- Learning curve can be significant

- Licensing can be complex for smaller teams

- Advanced capabilities require skilled verification engineers

Platforms / Deployment

Linux / Windows for selected workflows

Self-hosted / Hybrid options vary

Security & Compliance

SSO/SAML, MFA, encryption, audit logs, RBAC: Varies by enterprise setup.

SOC 2, ISO 27001, GDPR, HIPAA: Not publicly stated.

Integrations & Ecosystem

Questa fits into Siemens EDA and broader semiconductor verification workflows. It can be used with regression systems, FPGA flows, formal tools, and enterprise verification environments.

- Siemens EDA ecosystem

- UVM verification environments

- Formal verification flows

- CDC and RDC tools

- FPGA design flows

- Verification management systems

Support & Community

Siemens provides documentation, training, enterprise support, and professional services. Questa has strong professional adoption in verification engineering communities.

#4 — Synopsys VCS

Short description: Synopsys VCS is a high-performance RTL simulation platform used for functional verification of ASICs, SoCs, and complex digital designs. It is widely used by semiconductor teams that need scalable simulation, coverage, and verification productivity.

Key Features

- High-performance RTL simulation

- SystemVerilog and UVM support

- Coverage-driven verification workflows

- Low-power verification support

- Debug integration with Synopsys tools

- Regression and verification flow support

- Suitable for large digital designs

Pros

- Strong performance for large simulation workloads

- Mature use in enterprise ASIC verification flows

- Good ecosystem alignment with Synopsys design tools

Cons

- Requires strong verification skills

- Enterprise licensing may be costly

- Best used as part of a structured verification environment

Platforms / Deployment

Linux

Self-hosted / Hybrid options vary

Security & Compliance

SSO/SAML, MFA, encryption, audit logs, RBAC: Varies by enterprise infrastructure.

SOC 2, ISO 27001, GDPR, HIPAA: Not publicly stated.

Integrations & Ecosystem

VCS is commonly used with Synopsys debug, coverage, formal, and design tools. It supports professional verification environments and large regression workloads.

- Synopsys verification ecosystem

- UVM and SystemVerilog flows

- Coverage tools

- Low-power verification

- Regression environments

- Debug and waveform tools

Support & Community

Synopsys provides enterprise documentation, customer support, training, and professional services. The tool has a strong user base among verification engineers and semiconductor companies.

#5 — Cadence Virtuoso

Short description : Cadence Virtuoso is a custom IC design platform used for analog, mixed-signal, RF, and custom layout workflows. It is widely used by analog designers, custom IC teams, semiconductor companies, and research organizations.

Key Features

- Analog and custom IC schematic design

- Custom layout editing

- Mixed-signal design workflows

- RF design support

- SPICE simulation integration

- Physical verification flow support

- Foundry process design kit support

Pros

- Strong standard for analog and custom IC design

- Deep ecosystem for foundry-based workflows

- Useful for complex analog, RF, and mixed-signal design

Cons

- Expensive and specialized

- Requires experienced analog and layout engineers

- Not ideal for simple digital-only design learning

Platforms / Deployment

Linux

Self-hosted / Hybrid options vary

Security & Compliance

SSO/SAML, MFA, encryption, audit logs, RBAC: Varies by enterprise deployment.

SOC 2, ISO 27001, GDPR, HIPAA: Not publicly stated.

Integrations & Ecosystem

Virtuoso is part of a broad custom IC and mixed-signal design ecosystem. It is commonly used with simulation, layout verification, foundry PDKs, and design data management workflows.

- Foundry PDK support

- SPICE simulation workflows

- Physical verification tools

- RF and analog design flows

- Mixed-signal verification

- Cadence design ecosystem

Support & Community

Cadence provides professional support, documentation, training, and customer programs. Virtuoso has strong adoption among professional analog and mixed-signal engineers.

#6 — Synopsys PrimeTime

Short description=: Synopsys PrimeTime is a static timing analysis and signoff tool used to verify whether chip designs meet timing requirements before tape-out. It is best for digital ASIC and SoC teams working on timing closure and signoff-quality validation.

Key Features

- Static timing analysis

- Signoff timing verification

- Constraint validation

- Multi-corner multi-mode timing support

- ECO timing analysis

- Power-aware timing workflows

- Integration with digital implementation flows

Pros

- Strong signoff timing analysis capability

- Widely used in professional ASIC flows

- Important for timing closure and tape-out confidence

Cons

- Specialized tool with a focused use case

- Requires timing analysis expertise

- Enterprise licensing can be costly

Platforms / Deployment

Linux

Self-hosted / Hybrid options vary

Security & Compliance

SSO/SAML, MFA, encryption, audit logs, RBAC: Varies by enterprise infrastructure.

SOC 2, ISO 27001, GDPR, HIPAA: Not publicly stated.

Integrations & Ecosystem

PrimeTime is used near the end of digital implementation and signoff flows. It connects with synthesis, place-and-route, power analysis, constraints, and ECO workflows.

- Synopsys implementation ecosystem

- Timing constraints

- Standard cell libraries

- Parasitic extraction tools

- ECO flows

- Signoff verification workflows

Support & Community

Synopsys offers enterprise support, training, and technical documentation. PrimeTime is mainly used by experienced timing, implementation, and signoff engineers.

#7 — Cadence Innovus

Short description: Cadence Innovus is a digital implementation platform used for place-and-route, optimization, clock tree synthesis, and physical design closure. It is suited for ASIC and SoC implementation teams building complex digital chips.

Key Features

- Digital place-and-route

- Timing-driven optimization

- Clock tree synthesis

- Power and area optimization

- Physical design closure

- Advanced-node implementation support

- Integration with Cadence signoff and verification tools

Pros

- Strong physical implementation capability

- Good fit for advanced digital chip design

- Useful in Cadence-centered ASIC flows

Cons

- Requires skilled physical design engineers

- Complex for small or beginner teams

- Best value is seen in full enterprise flows

Platforms / Deployment

Linux

Self-hosted / Hybrid options vary

Security & Compliance

SSO/SAML, MFA, encryption, audit logs, RBAC: Varies by enterprise setup.

SOC 2, ISO 27001, GDPR, HIPAA: Not publicly stated.

Integrations & Ecosystem

Innovus connects with Cadence digital design, timing, power, verification, and signoff workflows. It is commonly used in production ASIC implementation environments.

- Cadence digital implementation flow

- Static timing analysis tools

- Power analysis tools

- Physical verification tools

- Constraint management

- Foundry and library workflows

Support & Community

Cadence provides technical support, documentation, training, and professional services. Innovus is mostly used by professional physical design teams.

#8 — AMD Vivado Design Suite

Short description : AMD Vivado Design Suite is used for FPGA design, synthesis, implementation, simulation, and debugging for AMD FPGA and adaptive SoC devices. It is best for FPGA engineers, embedded hardware teams, telecom teams, industrial systems, and prototyping use cases.

Key Features

- FPGA design and implementation

- RTL synthesis

- Timing analysis

- IP integration

- Hardware debugging

- Simulation workflows

- Support for AMD FPGA and adaptive SoC devices

Pros

- Strong toolchain for AMD FPGA development

- Good for FPGA prototyping and hardware acceleration

- Integrated IP and implementation flow

Cons

- Focused on AMD FPGA ecosystem

- Can be resource-intensive

- Learning curve can be high for advanced FPGA designs

Platforms / Deployment

Windows / Linux

Self-hosted desktop / workstation deployment

Security & Compliance

SSO/SAML, MFA, encryption, audit logs, RBAC: Not publicly stated.

SOC 2, ISO 27001, GDPR, HIPAA: Not publicly stated.

Integrations & Ecosystem

Vivado integrates closely with AMD FPGA devices, IP, embedded processing flows, and hardware debugging workflows.

- AMD FPGA IP catalog

- Embedded design workflows

- Hardware debugging tools

- Simulation tools

- Board support packages

- FPGA prototyping workflows

Support & Community

AMD provides documentation, tutorials, support resources, training content, and community forums. The ecosystem is strong for FPGA designers using AMD devices.

#9 — Intel Quartus Prime

Short description: Intel Quartus Prime is an FPGA design software suite for designing, compiling, verifying, and programming Intel FPGA devices. It is used by FPGA engineers, embedded teams, communications engineers, and hardware developers building Intel FPGA-based systems.

Key Features

- FPGA synthesis and implementation

- Timing analysis

- IP integration

- Device programming

- Simulation workflow support

- Hardware debugging tools

- Support for Intel FPGA families

Pros

- Strong fit for Intel FPGA development

- Integrated workflow from design to programming

- Useful for embedded, telecom, and hardware acceleration projects

Cons

- Focused on Intel FPGA ecosystem

- Advanced designs require FPGA expertise

- Large designs can require strong workstation resources

Platforms / Deployment

Windows / Linux

Self-hosted desktop / workstation deployment

Security & Compliance

SSO/SAML, MFA, encryption, audit logs, RBAC: Not publicly stated.

SOC 2, ISO 27001, GDPR, HIPAA: Not publicly stated.

Integrations & Ecosystem

Quartus Prime works closely with Intel FPGA devices, IP libraries, embedded development workflows, and debugging tools.

- Intel FPGA IP catalog

- Embedded processor workflows

- Simulation tool support

- Timing analysis

- Hardware debug tools

- Board and device programming flows

Support & Community

Intel provides documentation, community forums, technical resources, and device-specific guidance. The community is strong among FPGA engineers using Intel devices.

#10 — OpenROAD

Short description : OpenROAD is an open-source digital ASIC physical design flow focused on RTL-to-GDS workflows. It is useful for research, education, open-source silicon projects, and teams exploring cost-effective digital implementation flows.

Key Features

- Open-source RTL-to-GDS flow

- Floorplanning and placement

- Clock tree synthesis

- Routing support

- Timing-driven physical design

- Integration with open-source design tools

- Useful for education and research workflows

Pros

- Free and open-source

- Valuable for learning and research

- Helps democratize access to digital implementation flows

Cons

- Not a direct replacement for enterprise signoff tools in advanced commercial designs

- Requires technical setup and flow knowledge

- Support depends largely on community and project maturity

Platforms / Deployment

Linux

Self-hosted / open-source deployment

Security & Compliance

SSO/SAML, MFA, encryption, audit logs, RBAC: Not publicly stated.

SOC 2, ISO 27001, GDPR, HIPAA: Not publicly stated.

Integrations & Ecosystem

OpenROAD is part of the growing open-source silicon ecosystem. It is often used with open-source HDL tools, libraries, academic flows, and research projects.

- Open-source RTL tools

- Open PDK workflows

- Timing and routing tools

- Academic research flows

- Community-driven improvements

- Script-based automation

Support & Community

OpenROAD has community-driven documentation, academic involvement, open-source contributors, and research ecosystem support. Formal enterprise support is limited compared with commercial EDA vendors.

Comparison Table

| Tool Name | Best For | Platform(s) Supported | Deployment (Cloud/Self-hosted/Hybrid) | Standout Feature | Public Rating |

|---|---|---|---|---|---|

| Synopsys Design Compiler | ASIC and SoC synthesis | Linux | Self-hosted / Hybrid options vary | Production-grade RTL-to-gate synthesis | N/A |

| Cadence Xcelium | RTL simulation and verification | Linux | Self-hosted / Hybrid options vary | Scalable simulation and UVM verification | N/A |

| Siemens Questa | ASIC, FPGA, and formal verification | Linux, Windows for selected workflows | Self-hosted / Hybrid options vary | Broad simulation and formal verification platform | N/A |

| Synopsys VCS | High-performance RTL simulation | Linux | Self-hosted / Hybrid options vary | Enterprise-scale functional verification | N/A |

| Cadence Virtuoso | Analog, RF, and custom IC design | Linux | Self-hosted / Hybrid options vary | Custom IC schematic and layout design | N/A |

| Synopsys PrimeTime | Timing signoff and closure | Linux | Self-hosted / Hybrid options vary | Static timing analysis signoff | N/A |

| Cadence Innovus | Digital physical implementation | Linux | Self-hosted / Hybrid options vary | Place-and-route for ASIC implementation | N/A |

| AMD Vivado Design Suite | AMD FPGA design and prototyping | Windows, Linux | Self-hosted | FPGA synthesis, implementation, and debug | N/A |

| Intel Quartus Prime | Intel FPGA design and programming | Windows, Linux | Self-hosted | FPGA implementation for Intel devices | N/A |

| OpenROAD | Open-source digital ASIC implementation | Linux | Self-hosted | Open-source RTL-to-GDS flow | N/A |

Evaluation & Scoring of IC Design & Verification Tools

The scores below are comparative and based on practical capability, adoption, ecosystem fit, usability, security signals, performance, support, and value. They are not public ratings and should not be treated as universal rankings.

| Tool Name | Core (25%) | Ease (15%) | Integrations (15%) | Security (10%) | Performance (10%) | Support (10%) | Value (15%) | Weighted Total (0–10) |

|---|---|---|---|---|---|---|---|---|

| Synopsys Design Compiler | 10 | 5 | 9 | 8 | 9 | 9 | 5 | 8.05 |

| Cadence Xcelium | 9 | 6 | 9 | 8 | 9 | 9 | 6 | 8.10 |

| Siemens Questa | 9 | 6 | 8 | 8 | 8 | 8 | 6 | 7.75 |

| Synopsys VCS | 9 | 5 | 9 | 8 | 9 | 9 | 5 | 7.85 |

| Cadence Virtuoso | 10 | 5 | 9 | 8 | 8 | 9 | 5 | 8.00 |

| Synopsys PrimeTime | 9 | 5 | 9 | 8 | 9 | 9 | 5 | 7.80 |

| Cadence Innovus | 9 | 5 | 9 | 8 | 9 | 9 | 5 | 7.80 |

| AMD Vivado Design Suite | 8 | 6 | 8 | 5 | 8 | 8 | 8 | 7.35 |

| Intel Quartus Prime | 8 | 6 | 8 | 5 | 8 | 8 | 8 | 7.35 |

| OpenROAD | 6 | 4 | 6 | 4 | 6 | 5 | 10 | 5.95 |

How to interpret the scores:

- A higher score means stronger overall fit across the listed criteria, not a universal winner.

- Enterprise IC tools score high in core capability, performance, and support, but lower in price/value for small teams.

- FPGA tools score well for device-specific development but are not full ASIC signoff platforms.

- Open-source tools score strongly on value but require more technical setup and self-guided support.

- Teams should validate tools using real RTL, constraints, IP blocks, verification environments, and signoff requirements.

Which IC Design & Verification Tools Tool Is Right for You?

Solo / Freelancer

Solo chip designers, FPGA consultants, or independent researchers should focus on cost, device support, learning curve, and project scope.

Good options include:

- AMD Vivado Design Suite for AMD FPGA projects

- Intel Quartus Prime for Intel FPGA projects

- OpenROAD for open-source ASIC learning and research

- Siemens Questa or commercial simulators if the project requires professional verification and budget allows

Freelancers usually do not need full enterprise ASIC implementation stacks unless working under a client’s established EDA flow.

SMB

Small semiconductor startups or design service firms need practical tools that support RTL, simulation, synthesis, verification, and implementation without wasting budget.

Good options include:

- Cadence Xcelium for simulation and verification

- Synopsys VCS for high-performance digital simulation

- Siemens Questa for simulation and formal verification needs

- AMD Vivado or Intel Quartus Prime for FPGA prototyping

- OpenROAD for early research or experimental flows

SMBs should evaluate licensing flexibility, cloud compute options, toolchain compatibility, foundry support, and IP integration before buying.

Mid-Market

Mid-market semiconductor teams usually need a structured design flow, regression automation, verification management, synthesis, timing closure, and physical implementation.

Good options include:

- Synopsys Design Compiler for synthesis

- Synopsys VCS for simulation

- Synopsys PrimeTime for timing signoff

- Cadence Xcelium for verification

- Cadence Innovus for physical implementation

- Siemens Questa for advanced verification needs

Mid-market teams should focus on flow consistency, verification closure, license planning, support quality, and integration with internal compute infrastructure.

Enterprise

Enterprise semiconductor companies need scalable, signoff-grade, secure, and well-supported design and verification platforms.

Good options include:

- Synopsys Design Compiler for synthesis

- Synopsys VCS for simulation

- Synopsys PrimeTime for timing signoff

- Cadence Xcelium for verification

- Cadence Innovus for physical implementation

- Cadence Virtuoso for analog/custom IC design

- Siemens Questa for simulation and formal verification

Enterprise buyers should involve design, verification, CAD, IT, security, procurement, and foundry teams during selection.

Budget vs Premium

For budget-focused users, OpenROAD, FPGA vendor tools, and selected academic or startup programs may be practical starting points. These options are useful for learning, prototyping, FPGA development, and research.

For premium needs, Synopsys, Cadence, and Siemens EDA tools are stronger choices. Premium tools make sense when the cost of chip failure, tape-out delay, or verification gaps is much higher than software cost.

Feature Depth vs Ease of Use

If ease of use matters most, FPGA vendor tools or open-source learning flows may be easier to start with, although advanced designs still need expertise.

If feature depth matters most, enterprise EDA tools such as Synopsys Design Compiler, Cadence Xcelium, Synopsys VCS, Cadence Innovus, Cadence Virtuoso, and Siemens Questa are stronger options.

IC design tools are generally complex by nature. The real goal is not only ease of use, but predictable results, flow quality, verification confidence, and tape-out readiness.

Integrations & Scalability

IC design tools must work across multiple flow stages. A weak integration can create delays, data mismatches, or signoff risk.

Important integration areas include:

- RTL design and version control

- Verification environments

- IP libraries

- Synthesis flows

- Place-and-route tools

- Static timing analysis

- Power analysis

- Formal verification

- Foundry PDKs

- Regression infrastructure

Scalability should include compute requirements, license availability, tool runtime, regression throughput, and support for large designs.

Security & Compliance Needs

IC design files contain valuable intellectual property. Security is a major concern for semiconductor companies, defense suppliers, automotive chip teams, AI accelerator companies, and design service providers.

Important checks include:

- Role-based access control

- Secure license management

- Isolated project environments

- Encryption for stored and transferred data

- Audit logs

- Secure remote access

- Access governance for contractors

- IP block protection

- Backup and recovery processes

- Export control requirements where relevant

For cloud or hybrid flows, teams should also review data residency, compute isolation, vendor security documentation, and contractual controls.

Frequently Asked Questions (FAQs)

What are IC Design & Verification Tools?

IC Design & Verification Tools are software platforms used to design, simulate, verify, implement, and sign off integrated circuits. They help teams reduce functional, timing, power, and manufacturing risks before silicon fabrication.

Are IC design tools different from PCB design tools?

Yes. PCB tools focus on printed circuit boards, while IC design tools focus on chips, RTL, gates, layouts, timing, verification, and semiconductor manufacturing preparation.

Which tools are used for RTL simulation?

Common RTL simulation tools include Cadence Xcelium, Synopsys VCS, and Siemens Questa. FPGA tools also include simulation support for device-specific development flows.

Which tools are used for logic synthesis?

Synopsys Design Compiler is a widely recognized synthesis tool. FPGA workflows use synthesis inside vendor tools such as AMD Vivado and Intel Quartus Prime.

Which tool is used for analog IC design?

Cadence Virtuoso is widely used for analog, mixed-signal, RF, and custom IC design. It is commonly used with foundry PDKs and SPICE simulation workflows.

What is formal verification?

Formal verification uses mathematical methods to prove whether certain design properties are true or false. It helps find deep bugs that may be difficult to catch through simulation alone.

What pricing models are common for IC design tools?

Commercial IC design tools commonly use enterprise licenses, floating licenses, token-based licensing, module-based pricing, and support contracts. Pricing is usually customized based on tool scope, users, and deployment model.

Are open-source IC design tools good enough?

Open-source tools can be useful for learning, education, research, and some digital design experiments. For advanced commercial chips, enterprise signoff and foundry-qualified flows are often required.

How long does onboarding take for IC design tools?

Onboarding can take weeks or months depending on flow complexity, team skill, compute setup, licensing, libraries, PDKs, and verification environment maturity.

What are common mistakes when choosing IC design tools?

Common mistakes include choosing tools without testing real design data, ignoring verification closure, underestimating compute needs, skipping security review, and not confirming foundry or IP compatibility.

Can FPGA tools replace ASIC design tools?

FPGA tools are useful for FPGA development and prototyping, but they do not fully replace ASIC synthesis, physical design, timing signoff, or foundry-based manufacturing workflows.

What is timing signoff?

Timing signoff verifies whether a chip design meets timing requirements across operating conditions. It is essential before tape-out because timing failure can cause silicon malfunction.

How important is tool integration in IC design?

Tool integration is critical. IC design flows depend on smooth movement of data between RTL, simulation, synthesis, physical design, timing, power, verification, and signoff stages.

Is cloud EDA safe for chip design?

Cloud EDA can be safe when access control, encryption, project isolation, audit logging, and contractual protections are strong. Teams should review security carefully before moving sensitive design workloads to cloud infrastructure.

Conclusion

IC Design & Verification Tools are essential for building reliable chips, but the best tool depends on the design type, team size, budget, verification needs, and tape-out goals. Synopsys Design Compiler, Synopsys VCS, and Synopsys PrimeTime are strong choices for synthesis, simulation, and timing signoff. Cadence Xcelium, Cadence Virtuoso, and Cadence Innovus are powerful options for verification, custom IC design, and digital implementation. Siemens Questa is valuable for simulation, formal, and verification management. AMD Vivado and Intel Quartus Prime are practical for FPGA design and prototyping, while OpenROAD is useful for open-source silicon learning and research.